Przetłumaczyli: Gbbsoft i A'Tox

Standard S-9.1

(Określa podstawy elektryczne komunikacji w standardzie NMRA DCC)

Komunikacja z Centralki Sterującej do Dekodera Cyfrowego opiera się na przesyłaniu serii bitów, które składają się w instrukcje. Bit to sygnał, który reprezentuje jedną z dwóch wartości: "1" albo "0". Ta część standardu określa charakterystyki sygnału elektrycznego, który koduje bity.

A: Metoda kodowania bitów

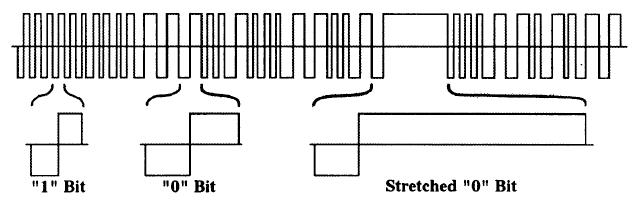

Sterowanie cyfrowe NMRA DCC opiera się na przesyłaniu serii zmian pomiędzy dwoma równymi poziomami napięcia o przeciwnej polaryzacji (1) (czyli raz płynie prąd +/-, który zmienia się w -/+, który zmienia się w +/i itd). Każda co druga zmiana polaryzacji oddziela jeden bit od drugiego. Druga zmiana polaryzacji dzieli każdy bit na pierwszą i drugą część (dwie zmiany przypadają na jeden bit). Centralki Sterujące powinny kodować bity w sygnale sterowania cyfrowego poprzez zmianę czasu trwania części bitów lub częstotliwości zmian polaryzacji.

Bity "0" i "1" kodowane są przez centralkę poprzez odległość pomiędzy zmianami polaryzacji (dwie kolejne zmiany - dwie części bitu).

Dla bitu "1" pierwsza i druga część bitu powinny mieć równą długość i długość ta nominalnie powinna wynosić 58 mikrosekund (2) dając całkowitą długość trwania bitu 116 mikrosekund. Centralka Sterująca powinna transmitować bity "1", w których czas trwania pierwszej oraz drugiej części mieści się w granicach od 55 do 61 mikrosekund. Dekoder Cyfrowy musi akceptować bity, których czas trwania pierwszej oraz drugiej części mieści od 52 do 64 mikrosekund, jako poprawny bit o wartości "1".

Dla bitu "0" długość pierwszej i drugiej części powinna być większa b równa 100 mikrosekund. Aby zachować składową stałą sygnału na poziomie zero, tak jak w przypadku bitów "1", pierwsza i druga część bitu "0" są zwykle sobie równe. Centralka Cyfrowa powinna transmitować bit "0", w którym długość każdej części powinna mieścić się w zakresie od 95 do 9900 mikrosekund, tak aby całkowita długość trwania bitu "0" nie przekraczała 12000 mikrosekund. Dekoder Cyfrowy musi akceptować bity, których czas trwania pierwszej oraz drugiej części mieści od 90 do 10000 mikrosekund, jako poprawny bit o wartości "0". Rysunek 1 przedstawia przykład bitów kodowanych przy użyciu opisanej metody.

Dekodery Cyfrowe muszą akceptować bity "1", których czasy trwania części o polaryzacji dodatniej i ujemnej różnią się nie więcej niż o 6 mikrosekund.

(1) W momencie umieszczenia lokomotywy lub innego taboru na torze nie jest możliwe aby zdefiniować, z punktu widzenia Dekodera Cyfrowego, która część bitu posiada "dodatnią" polaryzację.

(2) Wszystkie pomiary czasu wykonano pomiędzy punktami przejścia sygnału przez poziom 0 woltów.

Zależności czasowe bitu Jeden

Dla Wzmacniacza - Wyjście pod obciążeniem:

| Zależność dla bitu Jeden | Wynik |

| Czas impulsu A <55 us lub Czas impulsu A >61 us | Źle |

| Czas impulsu A = Czas impulsu B | OK |

| |Czas impulsu A - Czas impulsu B| <=3 us | OK |

| |Czas impulsu A - Czas impulsu B| >3 us | Źle |

Dekodery Cyfrowe muszą akceptować:

| Zależność dla bitu Jeden | Wynik |

| Czas impulsu A >=52 us i Czas impulsu A <=64 us | OK |

| Czas impulsu A = Czas impulsu B | OK |

| |Czas impulsu A - Czas impulsu B| <=6 us | OK |

B: Kształt sygnału sterowania cyfrowego

Sygnał cyfrowy NMRA dostarczany do torów przez dowolny system DCC (Digital Command Control), mierzony na wyjściu Wzmacniacza, powinien mieć następującą charakterystykę, mierzoną w warunkach obciążenia w zakresie od stanu braku obciążenia do stanu ciągłego maksymalnego obciążenia dopuszczalnego dla danego urządzenia. Przejścia sygnału przez obszar ograniczony przez napięcia -4 wolty i +4 wolty(3) powinno zmieniać się 2,5 wolta/us. Sygnał ten może zawierać nie monotoniczne zniekształcenia przy przejściu przez poziom 0 woltów, zapewniać przy tm powinien amplitudę nie mniejszą niż +/- 2 wolty(4).

Dekodery Cyfrowe powinny być zaprojektowane aby poprawnie dekodować sygnały z przejściami których szybkość zmian jest 2,0 woltów/us lub szybsze w zakresie napięć od -4 wolty do +4 wolty. Dekoder Cyfrowy powinien poprawnie dekodować co najmniej 95% poprawnie zaadresowanych pakietów, jak to jest zdefiniowane w S-9.2, przy obecności szumu (i/lub sygnałów innego typu) powyżej 100 kHz o całkowitej amplitudzie mniejszej od jednej czwartej całkowitej amplitudy sygnału cyfrowego NMRA(5).

Właściwy kształt sygnału cyfrowego NMRA powinien być tak opracowany aby zminimalizować emisję elektromagnetyczną tak by duże makiety obsługiwane za pomocą opisanego standardu mogły spełnić odpowiednie wymagania oddziaływania elektromagnetycznego amerykańskiego Federalnej Komisji do spraw Komunikacji (US FCC)(6).

(3) 0 woltów jest punktem pomiędzy skrajnymi napięciami.

(4) Standard dopuszcza nakładające się sygnały inne niż NMRA na szynach dla innych potrzeb, zapewniając, że Dekoder Cyfrowy NMRA może odrzucać takie sygnały.

(5) Te pomiary wykonuje się dla Dekodera Cyfrowego elektrycnie połączonego do toru lub szyny akcesoriów.

(6) Wszystkie elementy systemu zgodnego z NMRA powinny spełniać wszystkie odnośne wymagania FCC i/lub CE.

C: Zakresy przesyłanej poprzez szyny mocy i zakresy napięć zasilania

Podstawowa metoda dostarczania zasilania dla operowania taborem oraz akcesoriami, która powinna być zapewniana przez Centrale Sterujące oraz Dekodery Cyfrowe, polega na prostowaniu bipolarnego (naprzemiennego) sygnału NMRA dostarczanego do Dekoderów Cyfrowych(7). Aby zapewnić zasilanie Dekoderów Cyfrowych zależności czasowe w transmisji bitów są dopuszczalne tylko w określonych zakresach (patrz S-9.2, sekcja C). Wartość skuteczna sygnału cyfrowego NMRA, mierzona na torze, nie powinna przekraczać więcej niż o 2 wolty(8) napięcie określone w standardzie S9 dla odpowiedniej skali(9). W żadnym wypadku szczytowa amplituda sygnału cyfrowego nie powinna przekroczyć +/- 22 woltów. Minimalna wartość amplitudy sygnału cyfrowego NMRA, potrzebna aby dostarczyć zasilanie do dekodera powinna mieć wartość +/- 7 woltów mierzoną na torze. Dekodery Cyfrowe dla wielkości "N" oraz mniejszych powinny być tak zaprojektowane aby wytrzymać stałe napięcie co najmniej 24 wolty mierzone na torze. Dekodery Cyfrowe przeznaczone dla wielkości większych od "N" powinny być tak zaprojektowane aby wytrzymać napięcie stałe co najmniej 27 woltów mierzone na torze.

(7)Inne źródła zasilania są akceptowalne, gdy części zasilające Cyfrowych Central Sterowania są zdolne do wytwarzania podstawowego sygnału dla toru oraz Dekodery Cyfrowe są zdolne do pracy z podstawowym sygnałem opisanym w tym standardzie.

(8)Dodane napięcie służy skompensowaniu spadku napięcia w Dekoderze Cyfrowym, ma to zapewnić osiągnięcie maksymalnego napięcia określonego w standardzie NMRA Electrical Standard (S-9) na szczotkach silnika.

(9)Należy zwrócić uwagę, aby każdy silnik narażony bezpośrednio na sygnał cyfrowy przez dłuższy czas miał napięcie startu, które przekracza amplitudę sygnału lub ma wystarczająco dużą impedancję w zakresie 4-9 kHz aby zredukować prąd do typowego poziomu pracy. Sprawia to, że należy zwracać uwagę na precyzyjne silniki typu "core-less can motors", które stanowią obciążenie o niskiej impedancji oraz na makiety NMRA, na których amplituda sygnału cyfrowego przekracza +/- 18 woltów.

Powyższy tekst odpowiada wersji dokumentu zatwierdzonego i opublikowanego przez NMRA w lipcu 2004 o sygnaturze S-9.1.